## Article

# Securing IoT Networks Using Machine Learning-Resistant Physical Unclonable Functions (PUFs) on Edge Devices

Abdul Manan Sheikh <sup>1,2,\*</sup>, Md. Rafiqul Islam <sup>2</sup>, Mohamed Hadi Habaebi <sup>2</sup>, Suriza Ahmad Zabidi <sup>2</sup>, Athaur Rahman bin Najeeb <sup>2</sup> and Mazhar Baloch <sup>1</sup>

<sup>1</sup> Department of Electrical Engineering and Computer Science, A'Sharqiyah University, Ibra 400, Oman; mazhar.baloch@asu.edu.om

<sup>2</sup> Department of Electrical and Computer Engineering, International Islamic University Malaysia, Kuala Lumpur 50728, Malaysia; rafiq@iium.edu.my (M.R.I.); habaebi@iium.edu.my (M.H.H.); suriza@iium.edu.my (S.A.Z.); athaur@iium.edu.my (A.R.b.N.)

\* Correspondence: abdul.manan@asu.edu.om

## Abstract

The Internet of Things (IoT) has transformed global connectivity by linking people, smart devices, and data. However, as the number of connected devices continues to grow, ensuring secure data transmission and communication has become increasingly challenging. IoT security threats arise at the device level due to limited computing resources, mobility, and the large diversity of devices, as well as at the network level, where the use of varied protocols by different vendors introduces further vulnerabilities. Physical Unclonable Functions (PUFs) provide a lightweight, hardware-based security primitive that exploits inherent device-specific variations to ensure uniqueness, unpredictability, and enhanced protection of data and user privacy. Additionally, modeling attacks against PUF architectures is challenging due to the random and unpredictable physical variations inherent in their design, making it nearly impossible for attackers to accurately replicate their unique responses. This study collected approximately 80,000 Challenge Response Pairs (CRPs) from a Ring Oscillator (RO) PUF design to evaluate its resilience against modeling attacks. The predictive performance of five machine learning algorithms, i.e., Support Vector Machines, Logistic Regression, Artificial Neural Networks with a Multilayer Perceptron, K-Nearest Neighbors, and Gradient Boosting, was analyzed, and the results showed an average accuracy of approximately 60%, demonstrating the strong resistance of the RO PUF to these attacks. The NIST statistical test suite was applied to the CRP data of the RO PUF to evaluate its randomness quality. The *p*-values from the 15 statistical tests confirm that the CRP data exhibit true randomness, with most values exceeding the 0.01 threshold and supporting the null hypothesis of randomness.

Academic Editors: Bin Hu, Jiacun Wang and Xiwang Guo

Received: 27 November 2025

Revised: 6 January 2026

Accepted: 8 January 2026

Published: 12 January 2026

**Copyright:** © 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the [Creative Commons Attribution \(CC BY\) license](#).

**Keywords:** cryptography; IoT; PUFs; CRPs; machine learning

## 1. Introduction

The Internet of Things (IoT) has revolutionized remote monitoring and control of systems by enabling the processing of real-time data from numerous sensing devices. Cisco estimated that approximately 500 billion IoT devices would be deployed by 2030 [1]. Intelligent interfaces allow these devices to interact, collect, communicate, and store data efficiently. A trusted ecosystem built on the principles of authentication, authorization, privacy, confidentiality, availability, and integrity is therefore essential to ensure secure data transactions [2,3]. IoT devices are often constrained by limited storage, processing,

sensing, and computing resources [4]. Moreover, the diversity of devices from multiple vendors deployed within IoT networks makes them particularly vulnerable to security threats, with device authentication emerging as a critical factor in maintaining trustworthy communication. Authenticating edge devices is as important as authenticating users to ensure that only legitimate devices gain access to IoT resources. Weakly secured devices can compromise the entire system, leading to severe financial and reputational consequences. The heterogeneous nature of IoT networks, combined with the resource limitations of edge devices, makes traditional authentication schemes impractical. These constraints underscore the need for innovative, lightweight authentication mechanisms tailored specifically to IoT environments [5].

IoT devices operating at the network edge remain highly vulnerable to cyber threats, including data breaches, hardware tampering, and denial-of-service attacks. Traditional cloud-based, centrally managed infrastructures often struggle to counter advanced risks, including Distributed Denial of Service (DDoS) attacks, Man-in-the-Middle (MiTM) intrusions, eavesdropping, and attacks powered by artificial intelligence [6]. To mitigate these risks more effectively, computational capabilities can be shifted closer to the network edge, enabling real-time threat detection and mitigation directly on devices rather than relying solely on remote cloud infrastructure. Cloud-assisted IoT takes advantage of the large storage capacity and powerful computing resources available in cloud platforms to process and analyze data. Large amounts of data are continuously sent from widely distributed IoT nodes and cloud servers experience processing delays, leading to higher latency and slower response times for the services delivered to network users.

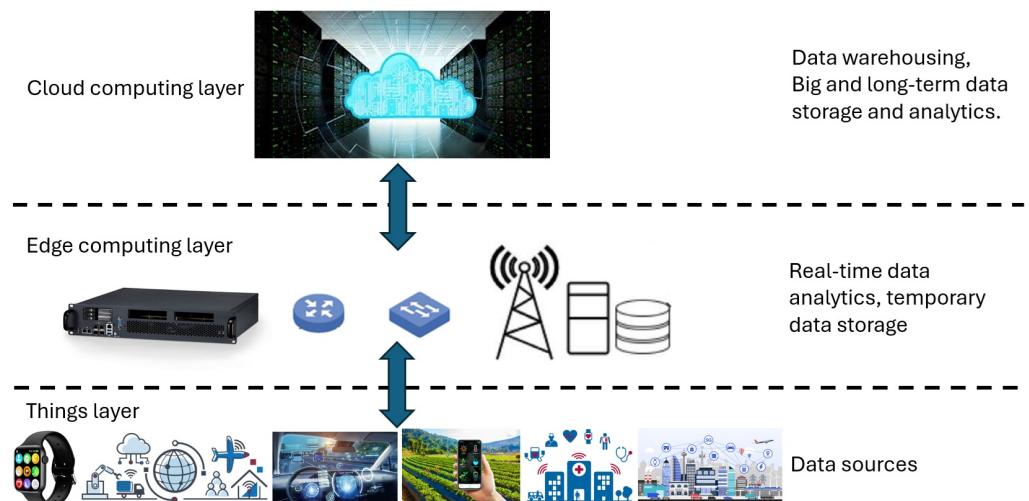

Edge Computing (EC) enables local processing and storage of sensitive data, thereby preserving privacy and facilitating faster access to critical information during security investigations [7]. In addition, EC offers advantages such as reduced latency, improved bandwidth efficiency, and enhanced privacy and security [8]. The EC architecture, shown in Figure 1, is typically organized into three layers: the edge devices layer, the edge nodes (or gateway) layer, and the cloud. Edge devices, such as IoT sensors, smartphones, cameras, or industrial machines, are primarily responsible for generating or collecting data. Due to limited processing capabilities, these devices typically perform only basic functions. The edge node layer consists of intermediate devices such as routers, edge servers, or micro data centers, which perform more advanced processing and data aggregation. This processing is further complicated by device heterogeneity and resource limitations. The cloud layer, in turn, handles complex computations, long-term data storage, and advanced analytics that exceed the capabilities of edge nodes. Connectivity among edge devices, edge nodes, and the cloud is supported through WiFi, 5G, or wired infrastructure to ensure efficient data transmission. Edge-driven IoT systems distribute heterogeneous resources across the network to achieve flexibility and scalability, supporting applications such as smart cities and autonomous vehicles. However, edge servers and devices remain constrained by limited power and processing capacity, and offloading large volumes of data and computational tasks can overload the network.

**Figure 1.** Edge computing architecture.

### 1.1. Motivations

The integration of EC with IoT introduces challenges due to inherent differences. IoT systems encompass a diverse range of hardware platforms and communication protocols, and their success depends on a unified framework that ensures seamless interoperability between IoT devices and edge nodes. Security and privacy remain primary concerns, complicated further by device heterogeneity and resource limitations such as memory capacity and battery power [9]. As a result, edge devices and servers are highly vulnerable to attacks, and a breach at any point can compromise the entire network. To address these risks, lightweight and robust security mechanisms tailored to the distributed and heterogeneous nature of IoT systems are essential. Several strategies have been proposed to mitigate security challenges in EC. Conventional measures include intrusion detection systems (IDS) to monitor malicious activity, strong access control to regulate permissions, encryption to protect data at rest and in transit, and authentication mechanisms to verify user and device identities. Beyond these methods, advanced technologies such as artificial intelligence (AI) and machine learning (ML) are increasingly used for real-time anomaly detection and adaptive defense against evolving threats [10]. Machine learning-based modeling attacks can learn and replicate the behavior of a PUF with high accuracy, thereby undermining its security. In contrast, blockchain-based approaches aim to ensure transaction integrity [8,11]. In parallel, Physical Unclonable Functions (PUFs) have garnered attention as hardware-based security primitives that provide device authentication, secure key generation, and cryptographic support. PUFs exploit manufacturing variations to generate unique device-specific identifiers that safeguard against cloning and other hardware-based attacks. Field Programmable Gate Arrays (FPGAs), known for their flexibility, reconfigurability, and rapid prototyping, are well-suited for implementing PUFs [12]. Moreover, PUFs can be integrated with intellectual property (IP) cores in FPGA-based systems, making them practical for real-world deployments [13,14].

Meanwhile, ML techniques such as Support Vector Machines, Logistic Regression, and Deep Neural Networks are increasingly used in hardware security to detect hardware Trojans, identify counterfeit integrated circuits (ICs), and evaluate the reliability of PUFs [15]. At the edge, ML models are also applied to analyze data streams and detect anomalies, intrusions, and malicious activities in real time. However, ML models deployed on resource-constrained edge devices are themselves vulnerable to adversarial threats, including poisoning attacks that corrupt training data, evasion attacks that deceive models with crafted inputs, inference attacks that extract sensitive information, and exploratory

attacks that exploit model weaknesses or replicate behavior. ML-based modeling attacks use ML methods to learn and reproduce the behavior of a PUF with very high accuracy, which can undermine its security. An adversary can construct a numerical model of the PUF by obtaining a portion of its challenge response pairs through eavesdropping or any other form of unauthorized access [16]. Adversaries typically exploit ML systems by targeting different stages of the learning pipeline. Training data can be poisoned to corrupt the learned model or to implant backdoors, while testing data may be manipulated to expose vulnerabilities and influence model predictions. In addition, privacy-oriented attacks aim to infer sensitive information from the trained model or its gradients [17]. Several studies have reported successful ML-based attacks on various types of physically unclonable functions, including RO-PUFs, using logistic regression and neural network-based models [18]. Among delay-based PUF architectures, RO-PUFs generally offer higher reliability than SRAM PUFs because their responses are less sensitive to environmental variations such as temperature and supply voltage. Although SRAM PUFs demonstrate strong resistance to modeling attacks, they are more susceptible to cloning and invasive attacks. To further enhance resistance against modeling, XOR PUFs introduce nonlinearity by combining the outputs of multiple identical PUF instances through an XOR operation, which makes them harder to model than single arbiter or ring oscillator PUFs. Nevertheless, when an optimal set of challenge-response pairs is available, XOR PUFs can still be effectively compromised using ML-based attacks [19]. These risks are exacerbated by the limited storage and computational capabilities of edge devices. To mitigate such vulnerabilities, integrating FPGA-based PUFs with ML frameworks offers a promising approach to strengthening edge security [20]. PUF-derived keys can be employed to encrypt ML models or authenticate devices contributing training data, protecting against tampering and data leakage. Leveraging FPGAs for PUF design provides flexibility, rapid prototyping, and reconfigurability, while seamless integration with other IP cores enables robust and scalable security solutions. The placement and routing of ring oscillators (ROs) on an FPGA play a critical role in determining the quality of PUF responses, as the physical locations of logic slices directly influence the inherent delay variations. Consequently, the oscillation frequencies of ROs are strongly dependent on their spatial distribution across the FPGA die. To counter machine learning-based modeling attacks, several mitigation strategies have been proposed, including the introduction of non-linearity into PUF architectures, XOR combination of multiple individual PUF responses, random selection of response substrings, and challenge randomization. While these approaches enhance resistance against modeling attacks, they often increase the architectural complexity of the PUF or complicate protocol-level protections, thereby impacting implementation efficiency and scalability [21].

### 1.2. Research Contributions

This research presents a comprehensive investigation into the design, implementation, and security evaluation of a RO-PUF on an FPGA, with an emphasis on ML-based modeling, resistance analysis, and statistical randomness analysis. The main contributions of this work are summarized as follows:

- **FPGA-Based Design and Implementation of RO PUF:** The study successfully implemented a configurable RO-PUF architecture on an FPGA platform. A dedicated testbench was developed to acquire large-scale challenge-response datasets under controlled operating conditions, verifying the reproducibility and uniqueness of the PUF behavior across multiple FPGA instances.

- **Comprehensive Evaluation of PUF Metrics:** The implemented RO PUF was analyzed using standard performance metrics such as uniformity, uniqueness, and reliability

(intra-Hamming distance). The proposed design demonstrated balanced uniformity near the ideal 50%.

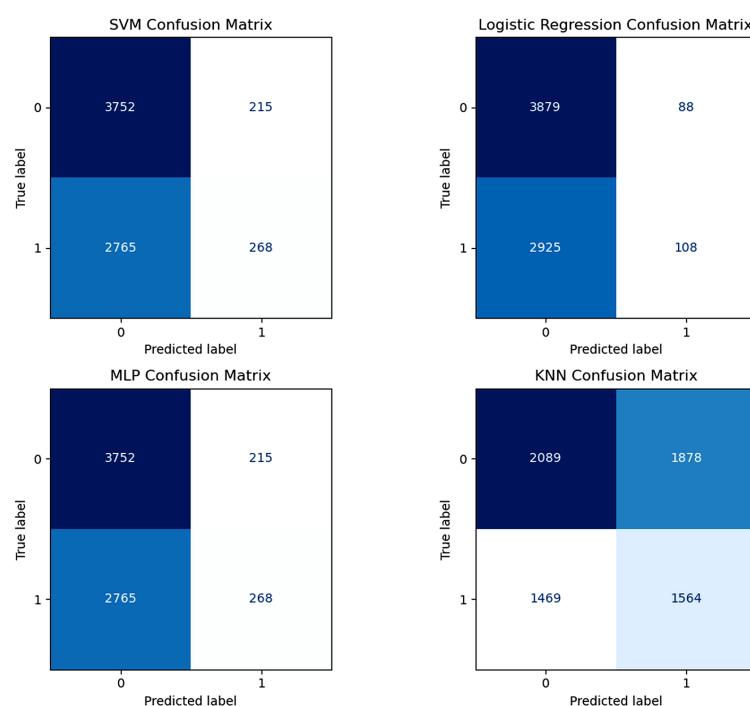

- Machine Learning-Based Attack and Accuracy Estimation: To assess the resilience of the proposed RO-PUF against modeling attacks, various ML algorithms, including Logistic Regression (LR), Support Vector Machine (SVM), Multilayer Perceptron (MLP), and k-Nearest Neighbor (k-NN), were employed. Confusion matrix analysis revealed that linear models, such as LR, failed to capture the nonlinear challenge-response relationship, while nonlinear models (SVM, MLP, and k-NN) performed moderately better but exhibited trade-offs between precision and recall. The findings confirmed that none of the models achieved strong predictive accuracy, highlighting the robustness and unpredictability of the proposed RO-PUF against ML-based cloning attempts.

- Randomness Validation Using NIST SP 800-22 test suite: The randomness quality of the generated CRP responses was validated using the NIST statistical test suite, covering tests such as frequency, runs, block frequency, and cumulative sums. The majority of the tests yielded  $p$ -values greater than 0.01, confirming that the PUF outputs exhibit strong statistical randomness and are suitable for cryptographic and authentication applications.

## 2. Related Works

Shen et al. proposed an integrated security framework for EC that combines ML and cryptographic techniques to monitor and detect abnormal activities on the network. The study provides valuable insights into the use of Support Vector Machine (SVM), k-Nearest Neighbor (k-NN), and Long Short-Term Memory (LSTM) models for time series prediction, evaluated using performance metrics such as precision, recall, and F1-score [22]. In the Collaborative Edge Computing (CEC) model, the edge layer handles data storage and processing in a distributed manner. Given the limited processing capacity of individual edge devices, these devices cooperate to offload tasks among themselves, a process known as load balancing. The researchers in [23] employed PUFs to authenticate edge devices during load balancing, eliminating the need to store a database of CRPs locally. Cheng et al. integrated blockchain technology with certificateless cryptography, elliptic curve cryptography, and pseudonym-based cryptography to enable mutual authentication between edge servers and IoT devices [24]. The study in [25] proposed a privacy-preserving edge computing approach that utilizes federated learning to train a unified deep learning model across multiple end users collaboratively. Instead of sharing raw data, only model parameters (i.e., gradients) are exchanged between participants. The parameters from local deep learning models on various edge nodes are aggregated at the edge and then distributed to all participants. Through several iterations of local training and parameter aggregation, a deep learning model is developed that preserves user privacy without the need to share raw data. Zhang and colleagues introduced a configurable tristate PUF that can operate as an arbiter PUF, a ring oscillator PUF, or a bistable ring PUF. The design uses a bitwise XOR-based obfuscation mechanism to hide the relationship between challenges and responses. As a result, machine learning models fail to build accurate prediction model, with all attack accuracies remaining between 50% and 60%, which is effectively the same as random guessing [26]. The authors of [27] introduced an authentication method that employs arbiter PUFs together with three protection strategies called challenge splitting, challenge scrambling, and challenge padding. Each strategy disrupts the structure or visibility of the challenge so that machine learning models cannot form an accurate numerical model of the PUF. In ref. [28], a hybrid secure deduplication scheme is introduced that ensures data privacy on the server side while enhancing network performance on the client side. Additionally, an additive homomorphic encryption method is proposed to enable

efficient deduplication operations on resource-constrained edge nodes. Intrusion detection systems (IDS) are vital for the security of IoT systems, as they detect traces of known attacks and unusual behavior in IoT devices and their connecting networks [29]. However, the majority of IDS algorithms use conventional encryption and cryptographic techniques. Unfortunately, these approaches are vulnerable to physical attacks, as they primarily rely on storing secret keys in the device's local memory. Blockchain is considered an ideal approach to store the huge amount of data generated by IoT devices with utmost privacy and security using a distributed ledger. However, the resource-constrained IoT devices cannot meet the computational requirements of data mining in blockchain networks. Sarkar et al. have proposed a robust PUF-based authentication system to replace the popular consensus algorithms [30].

A PUF design based on Generalized Galois Ring Oscillators (GenGARO) was implemented on Artix-7 FPGAs, Advanced Micro Devices (AMD), Santa Clara, CA 95054, USA using both 11-LUT and 3-LUT configurations. The proposed design demonstrates strong resilience against various ML models, including Decision Trees (DT), Random Forests (RF), k-Nearest Neighbors (k-NN), Support Vector Machines (SVM), and Multilayer Perceptrons (MLP) [19]. Another approach, the Structure-Obfuscated PUF (SO-PUF), is built on a configurable ring oscillator (CRO) framework and dynamically removes NOT gates at each stage based on the challenge input. As reported in [31], SO-PUF was implemented on an Xilinx Spartan-6 FPGA, AMD, Santa Clara, CA 95054, USA and achieved near-random prediction accuracy. Kareem et al. [32] investigated the vulnerability of three RO-PUF designs to ML attacks and evaluated their prediction accuracy using models such as DT, RF, k-NN, and SVM. Abulibdeh et al. introduced the Algorithmically Optimized Configurable Ring Oscillator PUF (AOCRO), which demonstrated strong resistance to ML modeling attacks. In their evaluation, five different ML algorithms (SVM, MLP, LR, CNN, and CMA ES) were trained on a dataset of one million CRPs, achieving an average prediction accuracy of 61.3%, indicating enhanced robustness compared to conventional CRO PUF designs [33]. Jack Miskelly et al. investigated the impact of ML attacks on Configurable RO PUFs. The study simulated 128-bit CRO PUFs and multi-PUF variants with datasets ranging from 1000 to 10,000 CRPs. The results showed that conventional CRO PUFs could be accurately modeled using an LR, ML model, achieving prediction accuracies exceeding 98–99% [34]. Laguduva et al. proposed a non-invasive, architecture-independent attack on PUFs using CRPs. This method achieved a cloning accuracy of 93.5% without requiring any prior knowledge of the PUF's internal architecture [35]. A summary of the results obtained by the above-mentioned researchers is shown in Table 1.

**Table 1.** ML model accuracy (%) against RO PUFs.

| Article | KNN         | SVM         | MLP         | RF          | DT          | LR    |

|---------|-------------|-------------|-------------|-------------|-------------|-------|

| [19]    | 56.76–63.24 | 49.76–69.71 | 50.10–70.86 | 62.67–75.81 | 57.90–72.00 |       |

| [31]    |             | 49.75       | 63.13       |             |             | 49.63 |

| [32]    | 74.6        | 66.2        |             | 72.3        | 64.6        |       |

| [36]    |             | 56.64       | 58.04       |             |             | 51.9  |

| [37]    |             | 58.59–61.95 |             |             |             |       |

### 3. Physical Unclonable Functions (PUFs)

Researchers have identified PUFs as robust security primitives that can guarantee the three pillars of security, namely confidentiality, authenticity, and privacy, of IoT data. PUFs extract unique information from the physical characteristics of the IoT devices [38]. PUF-based authentication protocols enhance the security of resource-constrained edge devices without requiring them to store credentials in their limited non-volatile memory.

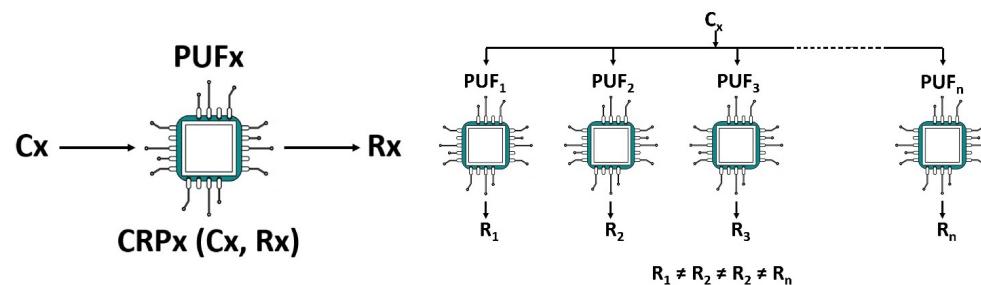

They utilize the inherent random variations introduced during manufacturing to generate secret keys dynamically. PUFs provide essential security functions such as authentication and secret key generation, especially in resource-constrained environments like the IoT [39]. The inherent unclonability of PUFs stems from numerous uncontrollable random parameters introduced during fabrication. When a PUF receives an input, known as a challenge (C), it produces a corresponding output response (R). Figure 2 illustrates that physical variations in the fabrication of integrated circuits (ICs) can result in two ICs yielding different responses to the same challenge. This relationship between the input and output is referred to as a CRP [40]. Traditional authentication methods rely on storing secret credentials in a device's memory, which makes them unsuitable for physically unprotected IoT devices. Attackers can exploit physical vulnerabilities to compromise the entire system. PUFs mitigate such risks in two key ways: first, they generate volatile secrets that are not stored in digital memory but are intrinsically embedded in the hardware structure; second, the uniqueness of each PUF enables it to serve as a unique identifier for individual IoT devices [41].

**Figure 2.** PUFs Challenge & Response Pair (CRP) generation [42].

### 3.1. PUFs Classification

PUFs can be placed into two groups based on the number of CRPs they can generate: strong and weak. The limited number of CRPs in a weak PUF is typically proportional to the number of components used in its construction. In contrast, strong PUFs provide a vast number of CRPs, making polynomial-time modeling attacks computationally impractical [43]. Strong PUFs are typically employed in authentication and key establishment protocols, whereas weak PUFs are mainly used for identification and secure key storage applications [44]. Examples of strong PUFs include the Arbiter PUF, the XOR Arbiter PUF, and the Lightweight PUF. In contrast, weak PUFs are represented by designs such as the SRAM PUF, Ring Oscillator (RO) PUF, Anderson PUF, Memristor PUF, Thyristor PUF, and One-Time Programmable (OTP) PUF [45]. Additionally, PUFs can be classified as silicon-based and non-silicon PUFs, depending on the manufacturing process adopted. Silicon PUFs rely on fabrication mismatches inherent in integrated circuits and can be further divided into delay-based PUFs and memory-based PUFs. In contrast, non-silicon PUFs are based on physical irregularities in systems composed of non-electronic components. Memory-based PUFs utilize the initial binary states of memory upon power-up, whereas delay-based PUFs exploit variations in signal propagation delays within circuits.

### 3.2. RO PUFs

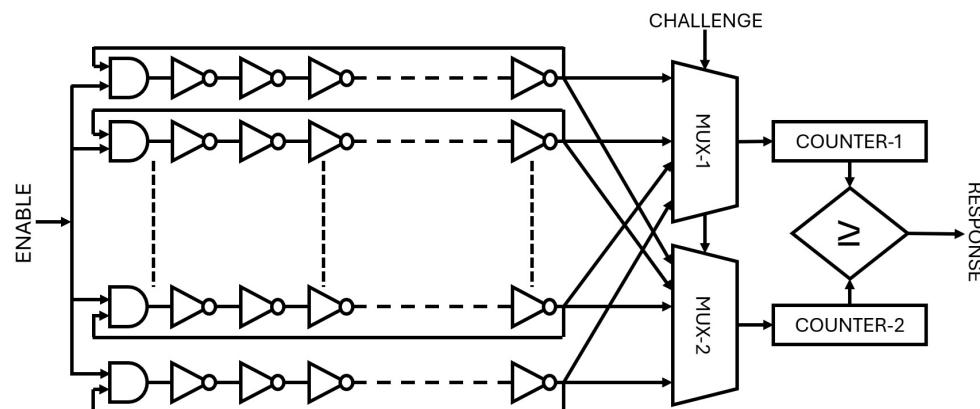

Due to inherent random variations in the manufacturing process, two similar ROs do not generate identical oscillation frequencies. The frequency differences between selected RO pairs form the output response of the PUF. An RO PUF consists of an odd number of NOT logic gates arranged in a ring, causing the output to oscillate between logic '1' and '0' at a specific frequency [46]. The basic architecture of an RO PUF, as shown in Figure 3, includes an odd number of inverter gates and an AND gate to enable or disable the feedback

loop. The conventional RO-PUF consists of several essential components:  $n$  ring oscillators (ROs), two  $n$ -to-1 multiplexers (MUXs), two counters, and a comparator circuit. The outputs of each RO are routed to the inputs of both MUXs, whose selected outputs serve as clock signals for the counters. Each counter increments according to the oscillation frequency of the specific RO selected by its respective MUX. Finally, the comparator compares the values stored in the two counters to produce the RO-PUF response corresponding to the applied challenge inputs. The frequency of each RO depends on the delay of the inverters, which is influenced by variations in the manufacturing process.

**Figure 3.** Ring Oscillator (RO) PUF.

The oscillation frequency of the RO PUF, as shown in Equation (1) is inversely proportional to both the odd number of gates ( $n$ ) and their average propagation delay ( $t_{pd}$ ). Consequently,  $f_{osc}$  is sensitive to inherent variations in gate delay, which causes each instance of the RO structure to exhibit a slightly different oscillation frequency [47].

$$f_{osc} = \frac{1}{2nt_{pd}} \quad (1)$$

The delay of each not gate is modelled by Equation (2), where  $\mu_{pd}$  is the nominal delay and  $\delta_k$  is a zero-mean random deviation, often approximated by gaussian,  $\mathcal{N}(0, \sigma_{pd}^2)$ .

$$t_{pd,k} = \mu_{pd} + \delta_k \quad (2)$$

The fundamental operation of the proposed RO PUF is outlined in Algorithm 1. Initially, multiple ROs are instantiated, each consisting of an odd number of inverters connected in a closed loop chain, causing continuous oscillation due to intrinsic gate delays. For every response bit, a corresponding challenge input selects a pair of ROs through multiplexers. The oscillation frequencies of two selected ROs are recorded over a fixed time interval using counters. If the first RO exhibits a higher count, indicating a higher oscillating frequency, a response bit of '1' is generated; otherwise, a '0' is assigned.

**Algorithm 1** Ring Oscillator PUF (RO-PUF) Algorithm

---

**Require:** Challenge input  $C = \{Sel_A, Sel_B\}$ , Time window  $T$

**Ensure:** Response bit  $R$

- 1: Initialize  $N$  Ring Oscillators:  $RO[0], RO[1], \dots, RO[N - 1]$

- 2: Initialize two  $N$ -to-1 MUXs, two Counters:  $Counter_A, Counter_B$ , and a Comparator

- 3: Select  $RO_A = RO[Sel_A]$  via MUX A

- 4: Select  $RO_B = RO[Sel_B]$  via MUX B

- 5: Connect  $RO_A$  output to  $Counter_A$  clock

- 6: Connect  $RO_B$  output to  $Counter_B$  clock

- 7: Enable  $Counter_A$  and  $Counter_B$  for fixed time window  $T$

- 8: During  $T$ , increment counters on each RO oscillation pulse

- 9: After  $T$ , disable both counters

- 10: **if**  $Counter_A > Counter_B$  **then**

- 11:      $R \leftarrow 1$

- 12: **else**

- 13:      $R \leftarrow 0$

- 14: **end if**

- 15: **return**  $R$

---

### 3.3. PUF Performance Metrics

PUF performance metrics serve as key indicators of functional behavior and security robustness. Hamming distance (HD) serves as a critical metric for measuring the degree of dissimilarity between two responses generated by a PUF and is further distinguished into intra-PUF and inter-PUF comparisons. The intra-PUF HD indicates the dissimilarity between the responses of a single PUF, highlighting the internal consistency or variability of the PUF. In contrast, the inter-PUF Hamming distance compares responses from two different PUFs, offering a gauge of the uniqueness and distinguishability of each PUF's responses. According to the classification presented by Pahlevi et al., the evaluation framework can be grouped into three main categories [48]. The first category, conventional PUF evaluations, includes metrics such as uniqueness, uniformity, and reliability. These metrics assess how distinguishable the responses are between different devices, how evenly distributed the output bits appear, and how consistently the PUF can reproduce the same response under varying environmental or operational conditions. The second category focuses on authentication-oriented metrics, which evaluate the practical suitability of PUFs for real-world security applications. Metrics such as the False Acceptance Rate (FAR) and False Rejection Rate (FRR) measure authentication accuracy, while bit aliasing and the bit error rate (BER) capture bit-level stability and possible device bias. Entropy estimation is also included in this category to quantify the randomness present in the response set. The third category comprises ML-based attack evaluations, which determine how well the PUF can withstand modern modeling attacks aimed at predicting its behavior.

The performance of access control mechanisms is evaluated using four fundamental metrics derived from the confusion matrix, which are defined in Equations (3)–(6): the false acceptance rate (FAR), the false rejection rate (FRR), the true acceptance rate (TAR), and the true rejection rate (TRR). The confusion matrix serves as a security evaluation tool for assessing the effectiveness and dependability of a PUF-based authentication system. FAR indicates instances where unauthorized individuals are mistakenly granted access, while FRR reflects cases where legitimate users are unfairly denied access, highlighting critical error dimensions that must be minimized [49].

$$FRR = \frac{\text{Number of False Rejections}}{\text{Total Number of Genuine Attempts}} \times 100\% \quad (3)$$

$$FAR = \frac{\text{Number of False Acceptances}}{\text{Total Number of Impostor Attempts}} \times 100\% \quad (4)$$

$$TRR = \frac{\text{Number of True Rejections}}{\text{Total Number of Impostor Attempts}} \times 100\% \quad (5)$$

$$TAR = \frac{\text{Number of True Acceptances}}{\text{Total Number of Genuine Attempts}} \times 100\% \quad (6)$$

The use of a confusion matrix to evaluate an authentication system highlights its importance in assessing how effectively the system differentiates between legitimate access attempts and potential security breaches.

- **Uniqueness:** It is used to quantify how different devices respond to the same input challenge. In other words, it is defined as the inter-device Hamming Distance (HD) between different devices, and its ideal value is 50%. The HD of Equation (7) estimates the uniqueness of CRPs, where  $n$  is the total number of devices,  $R_i$  and  $R_j$  are the respective responses of the  $i$ th and  $j$ th devices under the same challenge,  $HD(\cdot, \cdot)$  is the Hamming Distance operator, and  $m$  is the bit length of each response.

$$\text{Uniqueness} = \frac{2}{n(n-1)} \sum_{i=1}^{n-1} \sum_{j=i+1}^n \frac{HD(R_i, R_j)}{m} \quad (7)$$

- **Uniformity:** It is the probability that the 0 s and 1 s are uniformly distributed in PUF's response. Uniformity measures the balance between zeros and ones in the responses generated by a PUF. It is obtained by computing the average Hamming weight of the responses, as expressed in Equation (8).

$$\text{Uniformity} = \frac{1}{k} \sum_{l=1}^k R_l \quad (8)$$

- **Reliability:** It indicates the ability of a PUF to reproduce the same response bit for a given challenge input even when environmental conditions, such as supply voltage and temperature, vary. An ideal reliability close to 100% means that no bit flips occur across repeated measurements. However, achieving perfect reliability is difficult because PUF outputs are inherently sensitive to these variations.

$$HD_{\text{intra}}(R, R') = \sum_{b=1}^m |R_b - R'_b| \quad (9)$$

A standard metric for reliability is the intra-class Hamming Distance, which is illustrated in Equation (9), where  $R$  and  $R'$  are two responses from the same device under the same challenge.

- **Bit aliasing:** It complements uniqueness and uniformity by verifying whether a given bit exhibits enough variation. Ideally, each bit appears randomly as 0 or 1 with a typical value of 50%, signifying minimal bias. The aliasing factor for the  $b$ th bit is represented in Equation (10), where  $R_{i,b}$  is the  $b$ th bit of the  $i$ th device's response.

$$\text{Aliasing}(b) = \frac{1}{n} \sum_{i=1}^n R_{i,b} \quad (10)$$

- **Bit Error Rate (BER):** The BER defined in Equation (11) gives an estimate of how often a PUF produces incorrect or flipped bits when the same challenge input is applied

multiple times under varying environmental conditions, such as temperature and supply voltage.

$$\text{BER} = \frac{\text{Number of flipped bits}}{\text{Total bits measured}} \quad (11)$$

- Entropy: It is used to evaluate the overall randomness of PUF outputs, particularly against advanced modeling attacks and side channel attacks. A higher entropy value reflects a larger and more unpredictable response space. The most widely used metric for this purpose is Shannon entropy, which is defined in Equation (12) as follows:

$$H(R) = - \sum_{\omega} p(\omega) \log_2 p(\omega) \quad (12)$$

where  $\omega$  represents every possible output pattern, and  $p(\omega)$  denotes the probability associated with each pattern [40].

### 3.4. ML Modelling Attacks

Resistance and reliability against ML attacks are two major concerns for the overall viability of PUF-based authentication protocols [50]. ML-based attacks on PUFs can be classified as semi-invasive attacks, as adversaries exploit the PUF by intercepting the communication channel between the PUF client and the server. The intercepted data are then preprocessed, and a parametric numerical model is constructed using ML algorithms that can successfully predict PUF responses [51,52]. Adversaries carry out PUF modeling attacks using deep learning, LR, support vector machine, and evolution strategy, assuming access to CRPs [53]. Countermeasures against ML attacks on PUFs typically involve increasing the nonlinearity and complexity of the PUF model or integrating additional modules that enable more complex operating modes and communication protocols with the verifier [54].

#### Machine Learning

An ML model is developed by analyzing available training data on a computing platform. The presence or absence of labels, which represent target values, plays a critical role in model development. Based on the use of labels, ML methods are broadly classified into supervised and unsupervised learning approaches. Supervised learning relies on labeled training data, whereas unsupervised learning extracts patterns without requiring labels. In contrast, reinforcement learning employs automated feedback mechanisms to iteratively improve model behavior [55]. Each learning paradigm has distinct advantages and limitations, and no single technique can be considered universally optimal without considering application-specific constraints [56]. Like many transformative technologies, ML presents both significant opportunities and challenges. Its widespread adoption is expected to reshape the cyber threat landscape in the coming years. When integrated into malicious workflows, ML techniques can enable attacks that are more adaptive, more resilient, and less detectable by existing defense mechanisms, facilitating the emergence of novel threat vectors. Consequently, the application of ML in security systems introduces new attack surfaces that adversaries can exploit. In particular, several supervised learning algorithms are being investigated to optimize attack strategies and to automate tasks that traditionally require manual statistical analysis [57]. Identifying an appropriate ML model is a challenging task due to the availability of a wide spectrum of classification and regression strategies. Thus, picking a particular model involves evaluating key tradeoffs such as accuracy, computational efficiency, interpretability, and model complexity and often requires iterative experimentation. In this work, four supervised ML models are chosen for modeling DDoS attacks in IoT networks. These algorithms are examined to evaluate their

effectiveness in enabling more adaptive and intelligent attack strategies. A brief discussion of these models is presented below.

- Support Vector Machine (SVM): It identifies a hyperplane that best separates data points belonging to two different classes. In a two-dimensional feature space, this hyperplane is represented as a line, while in an n-dimensional space, where n denotes the number of features, it becomes a plane or higher dimensional decision boundary. Among the many possible separating hyperplanes, the SVM algorithm selects the optimal one by maximizing the margin between the two classes. Training an SVM directly on raw data often results in suboptimal performance due to issues such as missing values, outliers, and redundant information. Therefore, data preprocessing is essential and typically includes data cleaning to address missing values and outliers, followed by feature extraction or selection to retain the most informative attributes. When linear separation of classes is not feasible, kernel functions are employed to project the data into a higher dimensional space, where a clear separation becomes achievable [58,59].

$$y = f(x) = W^T x + b = \sum_{i=1}^N w_i x_i + b \quad (13)$$

SVM separates data across a hyperplane  $f(x) = 0$ , by solving a constrained quadratic optimization problem. The input data  $x_i$  ( $i = 1, 2, \dots, N$ ) consists of objects with different labels corresponding to the two classes, namely the positive and negative classes. Equation (13) represents a hyperplane that separates the given data. where N is the number of samples, W is an N-dimensional vector, and b is a scalar. The vector W and scalar b are used to define the position of the separating hyperplane.

- Multi-Layer Perceptron (MLP): is used as an Artificial Neural Network (ANN) classification algorithm. It belongs to a class of nonlinear statistical models comprising of multiple layers of nodes arranged in a directed graph, where each layer is fully connected to the subsequent layer. Typically, MLP consists of three types of layers, namely the input layer, one or more hidden layers, and the output layer. The output y of a neural model against input data  $x_i$  ( $i = 1, 2, \dots, N$ ) is shown in Equation (14).

$$y = f(W^T x) = f\left(\sum_{i=1}^N w_i x_i + b\right) \quad (14)$$

where f is the activation function, N is the number of neurons, W are the ANN model weights, and b is the bias vector.

- Logistic Regression (LR): Its a statistical modeling technique, commonly associated with the sigmoid function, that is used to predict a binary outcome based on one or more predictor variables. Binary logistic regression is applied when the dependent variable has two possible outcomes, while multinomial logistic regression is employed when the outcome variable consists of more than two categories [60]. The logistic regression model is expressed as logistic (sigmoid) function, in Equation (15).

$$\sigma(z) = \frac{1}{1 + e^{-z}} \quad (15)$$

where z is a linear summation of input features and their coefficients. As illustrated in Equation (16), the model predicts the probability p that the dependent variable y equals 1 given input x for binary classification.

$$p(x) = \frac{1}{1 + e^{-(\beta_0 + \beta_1 x)}} \quad (16)$$

where  $\beta_0$  is the intercept and  $\beta_1$  is the coefficient for the input feature. The odds of the event are expressed as  $\frac{p}{1-p}$ , in Equation (17), representing a linear relationship between the features and the log-odds [61].

$$\ln\left(\frac{p}{1-p}\right) = \beta_0 + \beta_1 x_1 + \beta_2 x_2 + \cdots + \beta_n x_n \quad (17)$$

- k-Nearest Neighbors (k-NN): It is a non-parametric ML algorithm applied to both classification and regression tasks. It assigns a class label or predicts a value for a query sample based on the majority class or the average value of its nearest neighbors in the feature space. The algorithm is simple to implement and does not require an explicit training phase. However, its performance deteriorates with high-dimensional data, and it incurs high inference time and memory overhead due to the need to store and compare all training samples. The k-NN algorithm operates in three main stages. First, it computes the distance between the query point and all training samples. Second, it selects the  $k$  closest neighbors based on the chosen distance metric. Finally, it predicts the class label or value of the query point using majority voting for classification or mean aggregation for regression.

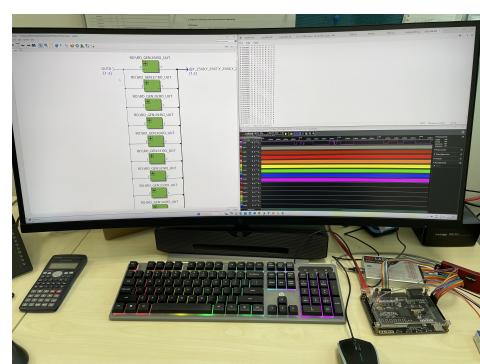

#### 4. Experimental Setup and Implementation

The experimental setup and synthesized netlist statistics of the proposed RO-PUF are shown in Figure 4. The proposed architecture is implemented and verified using Cyclone IVE FPGA chips (EP4CE10F17C8), Intel, Santa Clara, CA 95054, USA in the AX4010 development board. Intel Quartus Prime 18.1 Lite Edition, Santa Clara, CA 95054, USA is used to develop and verify the RO-PUF design prior to configuring the FPGA device. The Cyclone IV E EP4CE10F17C8 is a low-cost, low-power FPGA developed by Intel. It features 10,320 logic elements, 414 Kbits of embedded memory, 179 user I/O pins, and four PLLs for flexible clock management, all packaged in a 256-pin FBGA. The RO-PUF design, implemented in VHDL, is interfaced with the onboard GPIO pins of the AX4010 development board. All control signals, including challenge inputs and response outputs, are connected to a 16-channel logic analyzer through these GPIO pins. The design incorporates 512 ring oscillators (ROs) comprising five inverters. The outputs of the ROs are routed to two sets of 256-to-1 multiplexers (MUXes). Each MUX selects one RO output based on the challenge input, thereby determining which RO signal is passed to the output. The final response is generated by comparing the frequencies of two counters, Counter\_A and Counter\_B. An 8-bit linear feedback shift register (LFSR) is used to generate the challenge signals, based on the characteristic polynomial  $P(x) = x^8 + x^4 + 1$ .

(a) Experimental setup

| Parameters                | #                    |

|---------------------------|----------------------|

| Total logic elements      | 1071 / 10,320 (10 %) |

| Total registers           | 40                   |

| Total pins                | 12 / 180 (7 %)       |

| Max LUT depth             | 8.00                 |

| $f_{\max}$                | 94.23 MHz            |

| Worst case slack          | 9.388 ns             |

| Nominal core voltage      | 1.2 V                |

| Low junction temperature  | 0° C                 |

| High junction temperature | 85° C                |

(b) Post synthesis netlist statistics

Figure 4. FPGA implementation of proposed RO-PUF.

The ML hyperparameters listed in the Table 2 govern both the structural configuration and the learning behavior of a model. Their selection has a direct impact on convergence speed, generalization capability, and computational efficiency. Careful tuning of hyperparameters helps achieve an appropriate balance between underfitting and overfitting, increases robustness to noise, and improves predictive performance on previously unseen data. The ML models, such as SVM, LR, MLP, and k-NN, require careful parameter tuning to achieve optimal performance. For example, as illustrated in Table 3, SVM depends on the choice of kernel and gamma values, LR relies on regularization strength and iteration limits, MLP depends on hidden layer sizes, learning rates, and solver selection, while k-NN requires the selection of an appropriate number of neighbors and distance metrics. The training process involves preparing the PUF CRP dataset by separating the features from the responses and then splitting the data into training and testing sets for supervised learning. Validation and evaluation are carried out using metrics such as accuracy and confusion matrices to assess model performance. While train-test splits provide an initial measure of effectiveness, applying cross-validation techniques can further enhance reliability by reducing variance and ensuring the models generalize well to unseen CRPs.

**Table 2.** Hyperparameters of Machine Learning Models

| Model                        | Hyperparameters                                                                                                                                                                                            |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Support Vector Machine (SVM) | Kernel function, regularization parameter C, kernel coefficient gamma, polynomial degree, class weight, tolerance, shrinking heuristic                                                                     |

| Multilayer Perceptron (MLP)  | Number of hidden layers, number of neurons per layer, activation function, optimizer, learning rate, learning rate schedule, batch size, maximum epochs, L2 regularization alpha, momentum, early stopping |

| Logistic Regression (LR)     | Regularization type, regularization strength C, solver, maximum iterations, class weight, tolerance, multi-class strategy                                                                                  |

| K Nearest Neighbors (KNN)    | Number of neighbors k, distance metric, distance power p, weight function, search algorithm, leaf size                                                                                                     |

**Table 3.** Comparison of Machine Learning Models.

| Criterion                      | SVM            | MLP            | LR                   | KNN            |

|--------------------------------|----------------|----------------|----------------------|----------------|

| Learning type                  | Supervised     | Supervised     | Supervised           | Supervised     |

| Model nature                   | Margin based   | Neural network | Linear probabilistic | Instance based |

| Nonlinear capability           | kernels        | Yes            | No                   | Yes            |

| Interpretability               | Medium         | Low            | High                 | Medium         |

| Training complexity            | Medium to high | High           | Low                  | Very low       |

| Inference complexity           | Low            | Low            | Low                  | High           |

| Scalability                    | Medium         | High           | High                 | Low            |

| Overfitting risk               | Medium         | High           | Low                  | Medium         |

| Performance on small datasets  | High           | Low            | High                 | High           |

| High dimensional data handling | Excellent      | Good           | Good                 | Poor           |

#### 4.1. NIST Randomness Test

Randomness plays a fundamental role in cryptography, as the strength of many security mechanisms relies on the unpredictability of generated sequences. However, generating

truly random numbers is inherently challenging, and equally important is the rigorous evaluation of the quality of the generated data. To assess randomness, statistical tests are commonly employed, which yield a  $p$ -value. The  $p$ -value quantifies the probability that a truly random number generator would produce a sequence exhibiting less apparent randomness than the sequence under evaluation. In other words, it provides a statistical measure of how well the tested sequence aligns with the characteristics of an ideal random source.

Most empirical randomness tests, such as those included in the National Institute of Standards and Technology (NIST) Statistical Test Suite (STS), are built on the principles of statistical hypothesis testing. The NIST STS consists of 15 well-defined tests that evaluate binary sequences for signs of non-randomness. These tests analyze both local and global properties of the data. At the local level, they assess features such as the balance between zeros and ones, or the frequency of specific bit patterns within smaller segments of the sequence. At the global level, they examine broader statistical behavior across the entire bitstream to determine overall randomness. To further refine detection, the bitstream is often partitioned into multiple large segments, where each segment is analyzed independently. The results from these segments are then aggregated into final test statistics, which help to identify localized irregularities or systematic deviations from randomness. This multi-layered evaluation ensures that both subtle and significant weaknesses in the sequence can be detected, providing a comprehensive measure of its suitability for cryptographic applications.

In the context of the NIST STS, interpreting  $p$ -values is crucial. For each test, a significance level (commonly set at 0.01) is defined. If the  $p$ -value obtained from a sequence is greater than or equal to 0.01, the sequence is considered to have passed that particular randomness test, indicating no strong evidence of non-random behavior. Conversely, a  $p$ -value below 0.01 suggests that the sequence may deviate significantly from randomness. Ideally, when a large number of independent sequences are tested, the distribution of  $p$ -values across all tests should be uniform within the interval [0,1]. This uniformity demonstrates that the data behaves consistently with what is expected from a true random source. Therefore, both the proportion of sequences passing each test and the uniformity of their  $p$ -value distribution are essential criteria in validating the randomness of cryptographic data.

Each NIST STS test is defined by a specific test statistic, which falls into one of three categories:

- Bits: Analyzes characteristics such as proportion of bits, frequency of bit changes, and cumulative sums.

- m-bit blocks: Analyzes distribution of m-bit blocks ( $m < 30$ ) within the sequence or its parts.

- M-bit parts: Analyzes complex properties of M-bit parts ( $M > 1000$ ), such as matrix rank, sequence spectrum, or linear complexity.

Most tests are parameterized by  $n$  (sequence length) and may include a second parameter  $m$  or  $M$ , depending on the test. Table 4 summarizes the number of sub-tests included in the NIST STS suite. Notably, the non-overlapping template matching test has a variable number of sub-tests determined by  $m$  [62].

**Table 4.** Recommended bitstream parameters.

| #  | Name of the Test                  | <i>n</i>        | <i>M</i> or <i>m</i>                 | Sub-Test # |

|----|-----------------------------------|-----------------|--------------------------------------|------------|

| 1  | Frequency                         | $n \geq 100$    | —                                    | 1          |

| 2  | Frequency within a block          | $n \geq 100$    | $20 \leq M \leq n/100$               | 1          |

| 3  | Runs                              | $n \geq 100$    | —                                    | 1          |

| 4  | Longest run of ones               | $n \geq 128$    | —                                    | 1          |

| 5  | Rank                              | $n > 38,912$    | —                                    | 1          |

| 6  | Spectral                          | $n \geq 1000$   | —                                    | 1          |

| 7  | Non-overlapping Template Matching | $n \geq 8m - 8$ | $2 \leq m \leq 21$                   | 148        |

| 8  | Overlapping Template Matching     | $n \geq 10^6$   | —                                    | 1          |

| 9  | Maurer's Universal                | $n > 387,840$   | —                                    | 1          |

| 10 | Linear Complexity                 | $n \geq 10^6$   | $500 \leq M \leq 5000$               | 1          |

| 11 | Serial                            | —               | $2 < m < \lceil \log_2 n \rceil - 2$ | 2          |

| 12 | Approximate Entropy               | —               | $m < \lceil \log_2 n \rceil - 5$     | 1          |

| 13 | Cumulative Sums                   | $n \geq 100$    | —                                    | 2          |

| 14 | Random Excursions                 | $n \geq 10^6$   | —                                    | 8          |

| 15 | Random Excursions variant         | $n \geq 10^6$   | —                                    | 18         |

#### 4.1.1. Brief Description of NIST Randomness Tests

- Frequency (Monobit) test: Checks whether the number of ones and zeros is approximately equal.

- Frequency within a block test: Evaluates proportion of zeros and ones in *M*-bit blocks; expected frequency of ones is *M*/2.

- Runs test: Measures consecutive runs of zeros and ones; checks if transitions occur at expected frequencies.

- Longest run of ones in a block test: Examines if the longest run of ones (and zeros) in *M*-bit blocks matches the expected distribution.

- Random binary matrix rank test: Evaluates the rank of sub-matrices to detect linear dependencies in the sequence.

- Discrete Fourier Transform (Spectral) test: Detects periodic features using DFT peak heights.

- Non-overlapping template matching test: Detects excessive occurrences of aperiodic *m*-bit patterns using a sliding window that resets after each match.

- Overlapping template matching test: Counts occurrences of target substrings; window slides by one bit to allow overlaps.

- Maurer's Universal Statistical test: Measures compressibility of the sequence; overly compressible sequences indicate non-randomness.

- Linear complexity test: Estimates the length of the feedback register required to reproduce the sequence; shorter lengths indicate predictability.

- Serial test: Examines frequency of all overlapping *m*-bit patterns.

- Approximate Entropy test: Compares frequencies of overlapping *m*-bit and (*m* + 1)-bit patterns to detect regularity.

- Cumulative Sum (Cusum) test: Evaluates maximal deviation from zero in the cumulative sum of bits mapped to {−1, +1}.

- Random Excursions test: Measures the number of cycles with exactly *K* visits in cumulative sum random walks.

- Random Excursions Variant test: Analyzes frequency of visits to specific states in cumulative sum random walks to detect non-random patterns.

#### 4.1.2. Calibration

Calibration plays a critical role in ensuring the accuracy, reliability, and reproducibility of CRP acquisition when implementing PUFs on FPGAs. Since PUF responses are highly sensitive to environmental conditions such as temperature, voltage fluctuations, and aging, as well as to measurement artifacts including timing misalignment, noise, and signal distortions, calibration methods are employed to minimize errors before the data are fed into ML-based security models.

- **Timing Calibration:** Logic analyzers capture digital signals at high sampling rates ranging from hundreds of MHz to several GHz. However, any misalignment between challenge signals, response outputs, and control clocks can result in corrupted CRPs. The calibration strategies used to address these misalignment issues are discussed below.

- (i) Use a known reference signal, such as the FPGA internal clock or a test pattern generator, to align acquisition channels.

- (ii) Apply trigger-based synchronization in the logic analyzer to ensure consistent alignment of challenge vectors with corresponding responses.

- **Voltage and Signal Level Calibration:** FPGA output signals may degrade due to voltage drop, temperature variations, or I/O mismatches. This can cause the logic analyzer to misinterpret logical '0' and '1' levels. The calibration techniques adopted are,

- (i) Adjust threshold voltage levels on the logic analyzer to match FPGA I/O standards (e.g., LVTTL, LVCMOS).

- (ii) Periodically recalibrate using known test vectors to verify that digital transitions are accurately captured.

- **Environmental Calibration:** PUF responses are known to vary with temperature, supply voltage, and device aging. Environmental calibration ensures that CRPs remain stable and consistent under varying conditions. Calibration strategies include,

- (i) Use environmental profiling, where CRPs are collected across controlled temperature and voltage ranges, followed by applying corrective models.

- (ii) Apply ML-based preprocessing such as normalization or majority voting to compensate for environmental drift.

- **Noise Filtering and Signal Cleaning:** High-frequency noise or transient glitches can distort CRP acquisition and lead to unstable datasets. Techniques used in noise filtering and signal conditioning are,

- (i) Apply digital filtering techniques (e.g., glitch removal, debouncing) during data preprocessing.

- (ii) Perform repeated measurements followed by majority voting to ensure transient noise does not bias the dataset.

- **Data Alignment and Synchronization:** During multi-channel CRP acquisition, timing skew between channels can lead to incorrect challenge-response mapping. The calibration methods used for data alignment and synchronization include,

- (i) Perform multi-channel skew calibration by applying the same known signal to all acquisition channels and adjusting offsets accordingly.

- (ii) Use post-processing alignment algorithms to re-synchronize challenge-response mapping before ML training.

- **Statistical Calibration for ML Training:** Before feeding CRPs into machine learning models, statistical calibration ensures data integrity and uniformity for reliable analysis. The calibration techniques include,

- (i) Compute intra-class and inter-class metrics to evaluate the reliability and uniqueness of CRPs.

- (ii) Apply whitening techniques (e.g., Linear Feedback Shift Register (LFSR) or hash-based methods) to eliminate bias in raw PUF data.

- (iii) Normalize datasets to prevent ML models from being influenced by imbalanced or skewed response distributions.

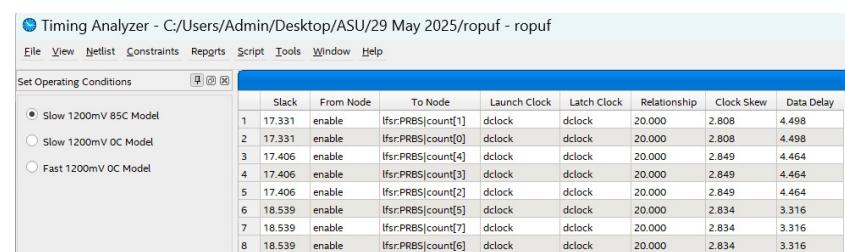

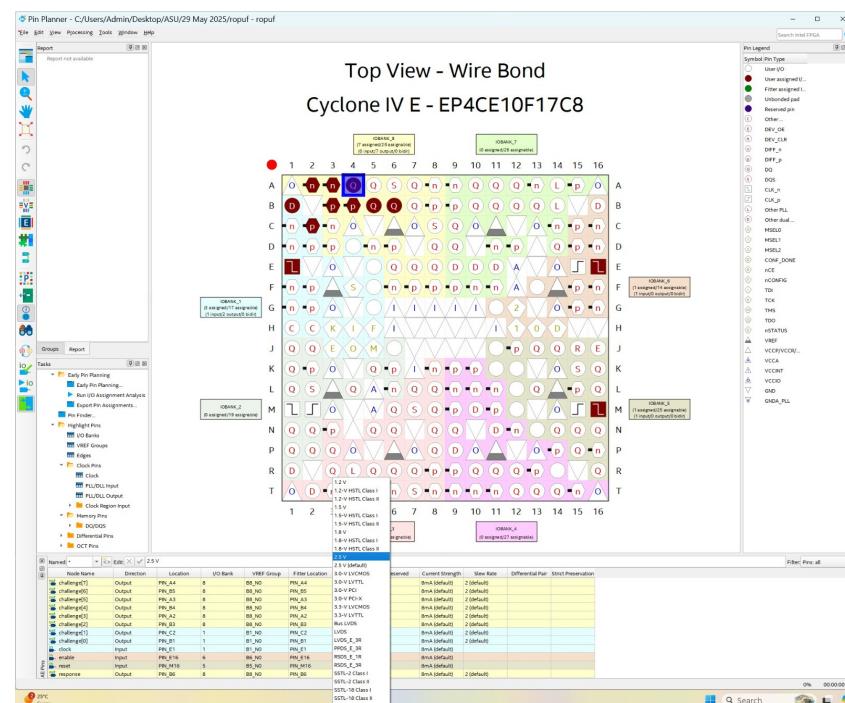

Intel Quartus Prime, illustrated in Figure 5, was employed to achieve timing alignment and voltage level adjustment, with on-chip phase-locked loops providing accurate clock alignment. The Timing Analyzer conducted static timing analysis across the entire design by evaluating specified data times, data arrival times, and clock arrival times in order to verify correct operation and identify potential timing violations. It establishes the timing relationships that must be satisfied for reliable system functionality. Signal synchronization across different clock domains is specified using Synopsys Design Constraints, including clock definitions and input-output delay constraints, to ensure positive setup and hold time margins. During implementation, the LVTTL IO standard was assigned to each pin through the Pin Planner, guaranteeing voltage compatibility with the external logic analyzer.

(a) Timing analyzer

(b) Pin Planner

Figure 5. Intel Quartus Prime Tools.

## 5. Results and Discussion

PUFs exploit the device's inherent physical randomness to generate unique and repeatable responses corresponding to challenge inputs. The key metric for measuring randomness, i.e., the balance between 0s and 1s in the output, is the relative frequency of bit 1 across all generated responses. This frequency provides a mathematical means to assess how uniformly bit 1 appears, which is critical in determining the PUF's effectiveness for security purposes. In security applications, high unpredictability and an even distribution of binary values are essential. As expressed in Equation (18), relative frequency is calculated by dividing the total number of 1s by the total number of response bits, thus providing an absolute indicator of the PUF's randomness and, by extension, its reliability and suitability for security applications.

$$p = \frac{1}{KL} \sum_{k=1}^K \sum_{l=1}^L b_{k,l} \quad (18)$$

where  $p$  and  $K$  represent the relative frequency of bit 1 in all responses and the total number of responses, while  $L$  denotes the response length. In contrast,  $k$  and  $l$  refer to the response  $k$ th and the position  $l$ th bit in the response output, respectively.

$$H = -\log_2 \max(p, 1-p) \quad (19)$$

Table 5 lists the uniqueness and uniformity values, which fall within the range of published RO PUF designs, but its reliability is noticeably lower than that of most prior works. However, lower reliability strengthens resilience against ML attacks as it introduces label noise into the challenge response pairs, making the PUF's input–output mapping harder to learn.

**Table 5.** Comparison of RO PUF metrics reported in the literature.

| Reference | Uniqueness                   | Uniformity                   | Reliability                  | Description                                                                                                              |

|-----------|------------------------------|------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| [63]      | 47.64%,<br>45.15%            | 49.8%, 48%                   | 98.5%, 96%                   | RO PUF using three and five stage oscillators on Artix seven FPGA with XOR and inverter logic.                           |

| [64]      | 50.1%                        | 49.45%                       | 98.33%                       | CLU-based design using XOR and XNOR to create a low hardware CRO PUF.                                                    |

| [65]      | 49.23%                       | 49.76%                       | 98.05%                       | A lightweight configurable RO PUF that combines RRAM with CMOS inverters.                                                |

| [66]      | 48.64%                       | 46.78%                       | 86%                          | Strong RO PUF (BST RPUF) designed for improved CRP count and stable responses.                                           |

| [67]      | 49.2%                        | 49.8%                        | 97.6%                        | RO PUF design used as a hardware security primitive for IoT applications.                                                |

| [68]      | 44.46%,<br>47.33%,<br>47.48% | 59.61%,<br>60.62%,<br>62.89% | 97.96%,<br>98.09%,<br>99.16% | Uses one hundred RO blocks with five, eleven, and twenty stages for response generation.                                 |

| [66]      | 48.64%                       | 46.78%                       | $\text{BER} < 10^{-9}$       | Highly reliable BST RPUF robust against ML-based modeling attacks.                                                       |

| This work | 49.1%                        | 56.86%                       | 60.13%                       | A configurable RO PUF architecture is implemented on an FPGA platform and its resilience against ML attacks is measured. |

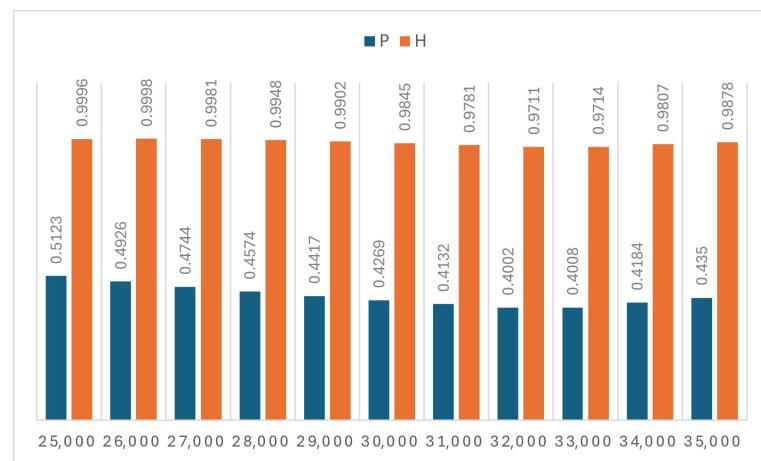

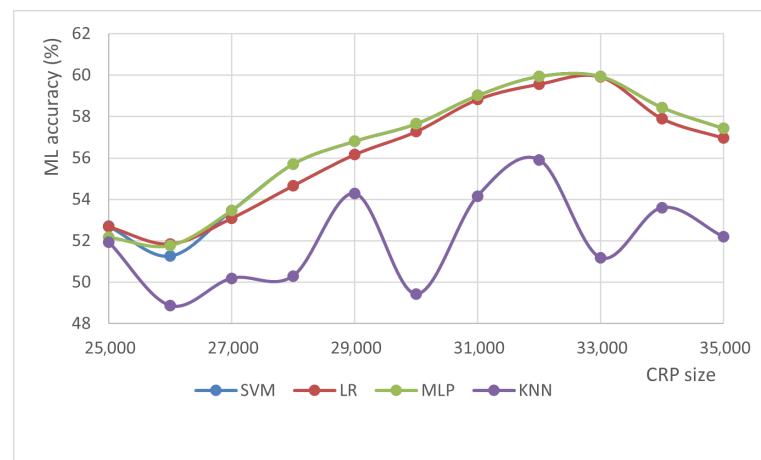

To assess the randomness of a bit sequence, Equation (19) defines  $H$  as the minimum entropy anticipated from PUF outputs to exhibit a uniform distribution.  $H$  peaks at 1 when  $p = 0.5$  and reaches its lowest at 0 when  $p = 0$  or  $p = 1$ . The optimal value of  $p$  is 0.5 for a binary system, as it produces the maximum entropy of 1 bit and represents the maximum uncertainty or randomness in a system. It also provides the strongest unpredictability and ensures resilience against cloning and prediction. The bitwise probability  $p$  and entropy  $H$  are plotted against varying CRPs in Figure 6. This study also conducts a vulnerability assessment of the proposed FPGA-based RO-PUF design against machine learning (ML) modeling attacks. The challenge-response pair (CRP) data is split into training and testing sets in an 80% to 20% ratio to build the attack model. This setup enables a clear and meaningful evaluation of the prediction accuracy of various ML models, with CRP lengths scaling up to 80,000. The graph shown in Figure 7 illustrates that the security of the PUF decreases as more CRPs become available. LR and MLP achieve the highest prediction accuracy, meaning they pose the most effective modeling threat, while the SVM also shows moderate attack capability. In contrast, k-NN performs poorly with low and unstable accuracy, indicating strong resistance against such attacks. Accuracy values rise with increasing challenge response pairs and peak around 32,000 to 33,000, after which improvements saturate or slightly decline. Since lower accuracy corresponds to stronger security, the physical unclonable function remains most robust against attacks with limited challenge response pairs and when weaker models like k-NN are used.

**Figure 6.** Bitwise probability (P) and entropy (H) against CRP numbers.

**Figure 7.** ML accuracy (%) versus varying number of CRP's.

The confusion matrix shown in Figure 8 evaluates the performance of a classification model. The top-left cell represents true positives (TP), indicating the positive instances correctly identified by the model. The bottom-left cell shows false positives (FP), which are negative cases incorrectly classified as positive, also known as type I errors. The top-right cell displays the number of false negatives (FN), referring to positive instances that were mistakenly predicted as negative. Finally, the bottom-right cell indicates true negatives (TN), where the model correctly identified negative instances. The sum of these four values gives the total number of predictions made by the model. Metrics such as accuracy, precision, recall, and F1-score can be derived from the confusion matrix to provide deeper insight into the model's performance. Equation (20) presents an estimation of model accuracy based on the values in the confusion matrix.

$$\text{Accuracy} = \frac{TP + TN}{TP + TN + FP + FN} \quad (20)$$

**Figure 8.** Confusion matrix of ML models (trained using 35K CRPs).

Modeling attacks has become a significant security concern, aiming to imitate the challenge-response behavior of PUFs and replicate their secret authentication keys. In the context of lightweight PUF-based systems, these attacks are generally classified into three main types: (a) machine learning (ML)-based software attacks, (b) side-channel attacks, and (c) hybrid attacks that combine ML techniques with side-channel analysis. A generic model, often polynomial, is used in ML-based modeling attacks for approximating CRP datasets. Adversaries divide the compromised CRP dataset into training and testing subsets. An iterative process is carried out in which challenges are input into the developed PUF model and the corresponding responses are predicted. The error between the predicted and actual response is used to estimate a loss function; subsequently, the model parameters are updated using optimization strategies such as gradient descent in logistic regression (LR) or maximum likelihood estimation for support vector machines (SVMs). Finally, the model's ability to replicate the actual PUF behavior is validated using the test set [69]. However, the effectiveness and precision of ML-based attacks decline as the structural complexity of the PUF increases. In particular, strong PUFs, such as Ring Oscillator (RO)

and Arbiter PUFs, which incorporate a high degree of nonlinear logic are more resistant to such modeling efforts.

### 5.1. Randomness Results

Table 6 summarizes the results of the NIST randomness tests conducted on the RO PUF CRP data. The  $p$ -value represents the likelihood that the observed bit sequence could have been produced by an ideal random source under the null hypothesis. In general, a sequence is considered random if its  $p$ -value exceeds the predefined significance level, typically 0.01, whereas values below this threshold indicate potential nonrandom behavior. It is important to emphasize that no single  $p$ -value alone confirms perfect randomness. Instead, a robust PUF should yield  $p$ -values that are uniformly distributed between 0 and 1 across various tests and sequences. Such a uniform distribution, along with the majority of  $p$ -values surpassing the 0.01 threshold, indicates that the CRP data exhibit statistical characteristics consistent with true randomness. Thus, it is concluded that the FPGA-based RO-PUF can effectively resist ML modeling attacks, as evidenced by the results in Table 7. The ML models perform no better than random guessing (50% accuracy for binary responses), and the RO-PUF successfully prevents learning patterns, given that the highest accuracy achieved is approximately 60%.

**Table 6.** RO PUF NIST statistical test results.

| Tests                             | $p$ -Values          |

|-----------------------------------|----------------------|

| Block Frequency                   | 0.444570             |

| Cumulative sums                   | 0.907298             |

| FFT                               | 0.561658             |

| Frequency Test                    | 0.583604             |

| Runs                              | 0.677681             |

| Longest run of ones               | 0.164698             |

| Rank                              | 0.945607             |

| Non overlapping Template matching | 0.51082702 (Average) |

| Overlapping template matching     | 0.711526             |

| Universal statistical             | 0.829717             |

| Approximate entropy               | 0.120839             |

| Random excursions                 | 0.332701             |

| Random excursions variant         | 0.447202222          |

| Serial test                       | 0.2013255            |

| Linear complexity                 | 0.420000             |

**Table 7.** ML model accuracy (%) against varying CRPs.

| Algorithm | 25K   | 26K   | 27K   | 28K   | 29K   | 30K   | 31K   | 32K   | 33K   | 34K   | 35K   |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| SVM       | 52.7  | 51.27 | 53.46 | 55.71 | 56.81 | 57.65 | 59.02 | 59.94 | 59.94 | 58.44 | 57.43 |

| LR        | 52.68 | 51.85 | 53.09 | 54.66 | 56.16 | 57.27 | 58.82 | 59.56 | 59.91 | 57.9  | 56.96 |

| MLP       | 52.17 | 51.77 | 53.46 | 55.71 | 56.81 | 57.65 | 59.02 | 59.94 | 59.94 | 58.44 | 57.43 |

| KNN       | 51.94 | 48.87 | 50.19 | 50.30 | 54.28 | 49.43 | 54.16 | 55.91 | 51.18 | 53.6  | 52.19 |

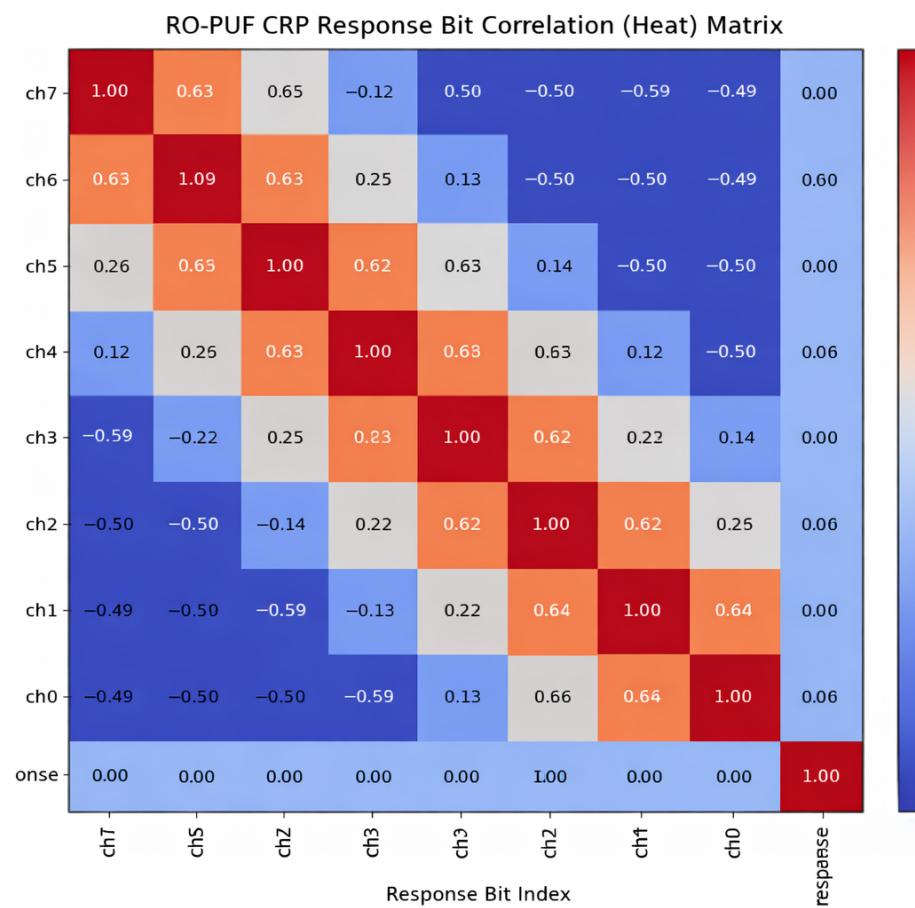

### 5.2. Correlation Matrix

The correlation matrix of the RO PUF CRP data in Figure 9 illustrates the degree of dependency between different output-bit values generated by the RO PUF. Each cell in the matrix represents a correlation coefficient between two response bits, ranging from  $-1$  to  $+1$ . The diagonal elements show perfect correlation (value of 1), indicating that each bit is fully correlated with itself.

**Figure 9.** RO PUF Correlation Matrix.

The colors transition from red along the diagonal to blue in the off-diagonal regions, reflecting varying levels of inter-bit correlation. From the heatmap, it can be observed that adjacent bits exhibit a moderate degree of correlation, while distant bits tend to be weakly correlated or nearly independent. This pattern suggests that neighboring ring oscillators may share certain environmental or structural influences, such as local routing, power distribution, or temperature variations, thereby introducing partial dependency among nearby bits. However, as the distance between bits increases, the influence diminishes, and the correlation between them approaches zero. The overall low inter-bit correlation indicates that the RO PUF produces outputs that are largely independent and random, thereby fulfilling one of the key requirements of a strong PUF design. The slight correlation observed between adjacent bits is expected in practical implementations due to physical proximity effects. To further enhance independence, post-processing techniques such as XOR-based bit mixing or improved oscillator placement strategies can be employed. In summary, the correlation matrix demonstrates that the RO PUF achieves good randomness and uniqueness characteristics, making it suitable for secure identification and authentication in hardware security applications.

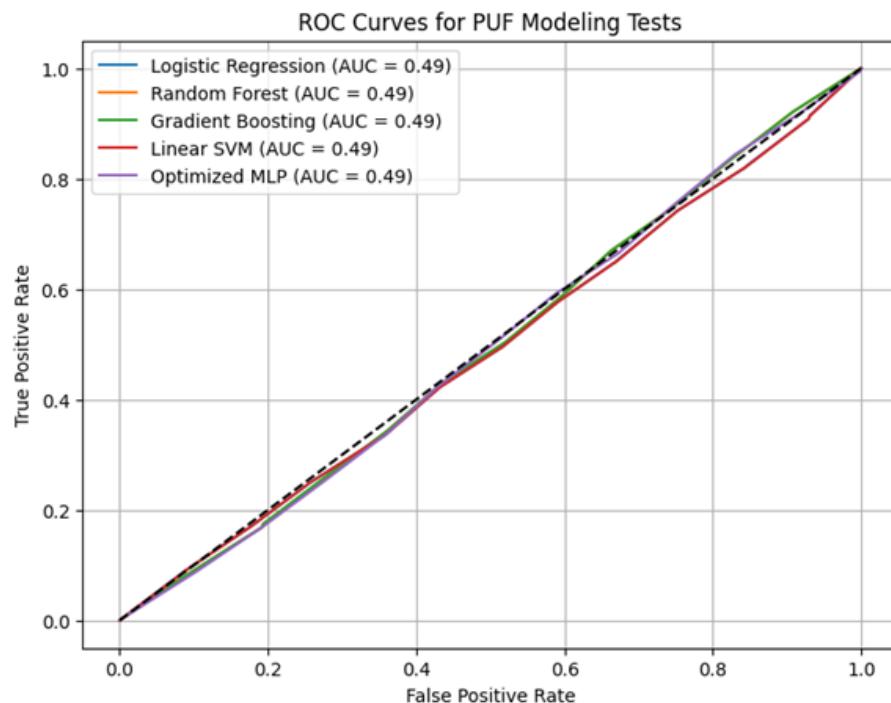

### 5.3. Receiver Operating Characteristic (ROC)

The ROC analysis for the RO-PUF in Figure 10 shows that all models—Logistic Regression, Random Forest, Gradient Boosting, SVM, and MLP—produced Area Under the Curve (AUC) values close to 0.49, with ROC curves nearly overlapping the diagonal reference line. This behavior indicates that none of the models could distinguish the RO-PUF responses from random guessing, thereby confirming its strong resistance to ML-based prediction. The intrinsic randomness and frequency-based variations of the oscillators

introduce complex, nonlinear behavior that conventional ML algorithms cannot capture effectively using standard training procedures.

**Figure 10.** Receiver Operating Characteristic of RO PUF.

#### 5.4. Deep Learning

Deep learning is a specialized branch of machine learning and artificial intelligence that employs multi-layered neural network architectures. In these models, data propagate through several successive layers, where early layers extract low-level features and deeper layers progressively combine them to form higher-level, more abstract representations. This hierarchical feature learning makes deep learning particularly effective for large-scale data analytics and statistical learning, such as the identification of cyber threats in intelligent and adaptive security systems. However, implementing large and complex deep learning models in edge computing environments remains challenging due to constraints on computation, memory, and energy resources [70]. Deep neural networks can approximate highly complex functions, with their representational power determined by the number of hidden layers and the number of neurons per layer. Among various deep learning architectures, Convolutional Neural Networks (CNNs) and Recurrent Neural Networks (RNNs) have demonstrated strong performance in many real-world applications [71]. CNNs are feedforward networks that exploit convolutional operations to automatically extract discriminative features from input data. A typical CNN architecture comprises convolutional layers, pooling layers for dimensionality reduction, and fully connected layers for classification, making CNNs highly effective for feature extraction and pattern recognition tasks [72]. In contrast, RNNs are designed with internal memory mechanisms that enable them to model temporal and sequential dependencies. By processing inputs in a sequence rather than independently, RNNs are well suited for applications involving time-dependent or ordered data [73].

As shown in Figure 11, a 1D CNN is developed using the Sequential API, comprising two Conv1D layers that successively extract low-level and then high-level temporal features, followed by a MaxPooling1D layer, which performs dimensionality reduction. The resulting feature maps are flattened and fed into a fully connected dense layer to

capture global relationships, while a dropout layer is incorporated to mitigate overfitting. The network concludes with a single-neuron output layer that generates a single prediction value, thereby making the model suitable for both regression and binary classification tasks. In addition, an RNN-based model employing a Long Short-Term Memory (LSTM) architecture is implemented to assess the learnability of the RO-PUF responses.

| Model: "sequential"          |                |         |

|------------------------------|----------------|---------|

| Layer (type)                 | Output Shape   | Param # |

| conv1d (Conv1D)              | (None, 8, 64)  | 256     |

| max_pooling1d (MaxPooling1D) | (None, 4, 64)  | 0       |

| conv1d_1 (Conv1D)            | (None, 4, 128) | 24784   |

| flatten (Flatten)            | (None, 512)    | 0       |

| dense (Dense)                | (None, 128)    | 65664   |

| dropout (Dropout)            | (None, 128)    | 0       |

| dense_1 (Dense)              | (None, 1)      | 129     |

| == Building RNN (LSTM) Model == |              |         |

|---------------------------------|--------------|---------|

| Layer (type)                    | Output Shape | Param # |

| lstm (LSTM)                     | (None, 64)   | 16896   |

| dense_2 (Dense)                 | (None, 64)   | 4160    |

| dropout_1 (Dropout)             | (None, 64)   | 0       |

| dense_3 (Dense)                 | (None, 1)    | 65      |

|                          |

|--------------------------|

| Total params: 90,753     |

| Trainable params: 90,753 |

| Non-trainable params: 0  |